写在前面:最近终于明白为什么这两年关于回忆录的内容少之又少——考试题量实在太大,而且每一分都拆得极细,0.5分、1分地计算,可谓“分难挣,题难做”。建议大家一定要提前刷题,直到真正形成题感,才能从容应对。

考试题型与形式

- 题型构成:选择题(含单选与多选)、计算题、分析题

- 考核方式:闭卷考试,允许携带计算器

务必记得带计算器,部分题目涉及复杂运算,手算极易出错或耗时过长。

选择题部分

选择题占比较大,但若复习充分,结合排除法基本可以应对。涉及知识点包括但不限于:冯诺伊曼体系结构、Cache失效率的定义与计算、CPI的含义及其求解方法、大端存储模式等。

个别题目较为偏门甚至令人困惑,例如:

- 麒麟芯片是否基于MIPS架构?(实际为手机芯片,采用ARM架构)

- 美国的芯片协议是否旨在保护本国芯片产业发展?(此表述存在争议)

- RV64是否使用64位指令长度?(错误,RISC-V所有标准指令均为32位)

这些题目提醒我们不仅要掌握基础知识,还需对主流技术架构有基本了解。

计算题内容

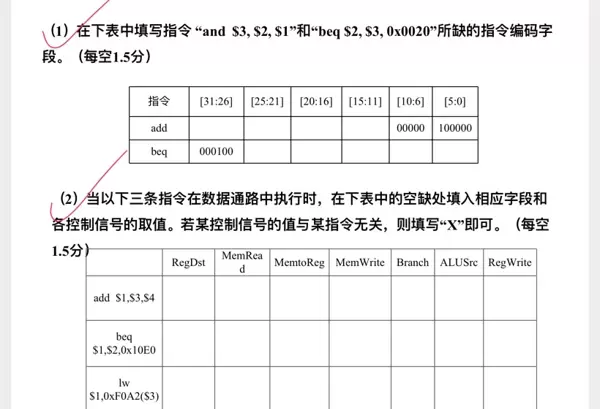

-

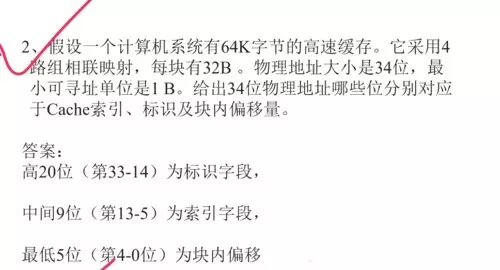

Cache组相联映射与地址转换

考察了虚拟地址到物理地址的转换过程。原题给出内存容量为64GB,页面大小为4KB,并提供了虚拟地址结构及页表编码信息,要求推导出对应的物理地址格式。

同时包含Cache组相联映射的设计,需明确各字段位数划分,例如标记位、组索引位、块内偏移位等。

-

Cache替换策略与命中判断

题目围绕Cache的访问流程展开,涉及替换算法(如LRU)、标记匹配以及是否命中等问题,需要根据给定访问序列进行状态追踪。

-

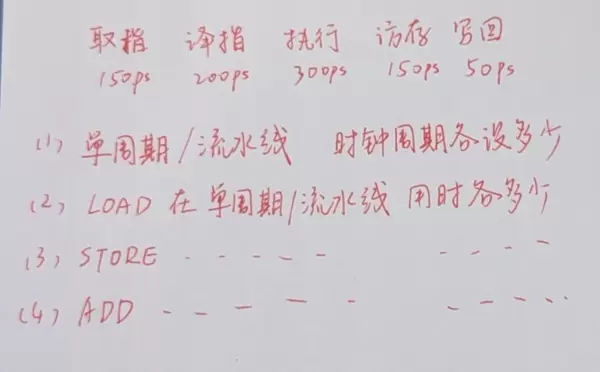

单周期与流水线时钟周期设计

该题为历年真题再现,重点在于理解不同指令类型在单周期和流水线结构下的执行时间差异,并据此确定合理的时钟周期长度。

-

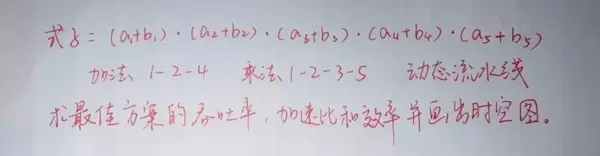

时空图与流水线三大性能指标

同样是经典真题类型,要求绘制指令执行的时空图,并计算吞吐率、加速比和效率三个关键参数。

-

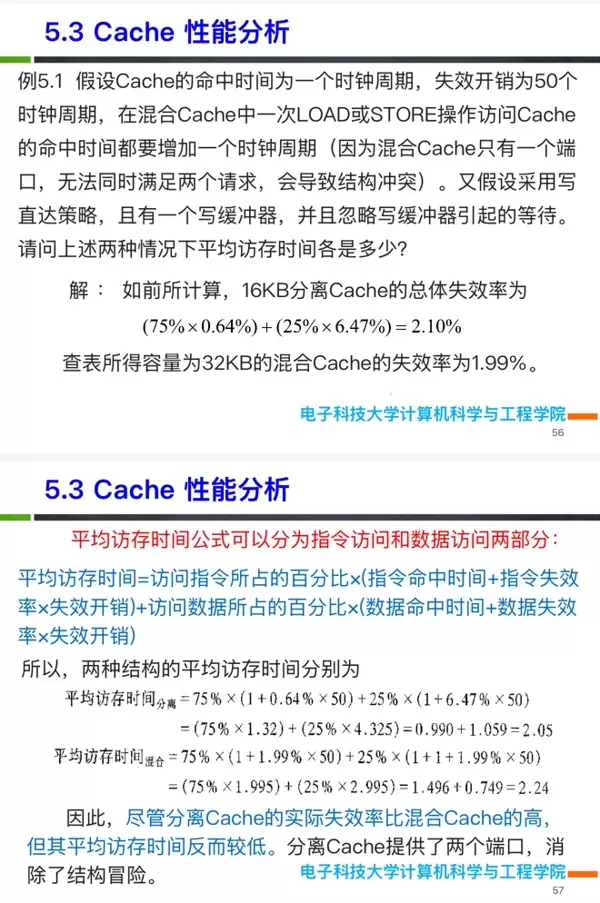

平均访存时间计算

几乎完全照搬往年原题,仅调整了个别数值。核心公式为:

AMAT = 命中时间 + 失效率 × 失效开销

分析题详解

-

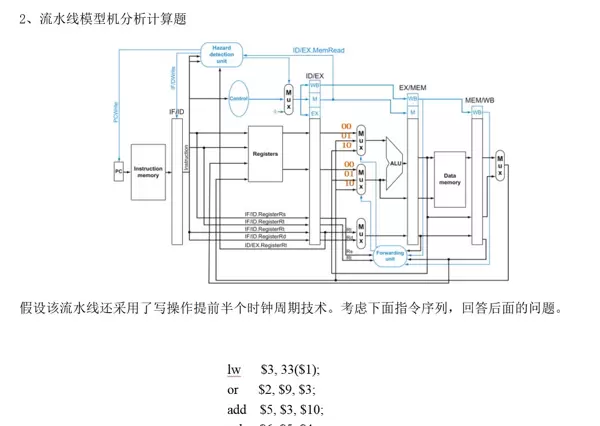

数据相关与流水线前推控制

题目设定六条连续指令共享同一寄存器,引发严重数据相关问题。处理过程中需综合运用前推(Forwarding)机制与插入气泡(Stall)策略,现场压力极大。

最终答案结构大致如下:

子问题包括:

(1)前推控制器信号设置:当lw指令处于WB阶段,且其后紧跟一个stall时,ALU输入端两个选择器的控制值及其他相关信号应如何配置?

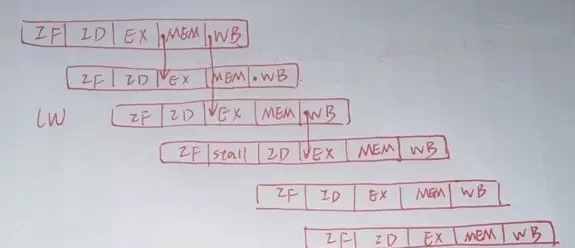

(2)绘制完整的流水线时序图(参考上图)

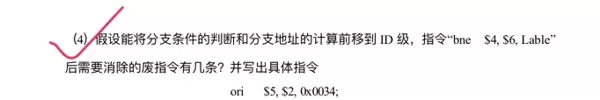

(3)分支提前处理逻辑分析

-

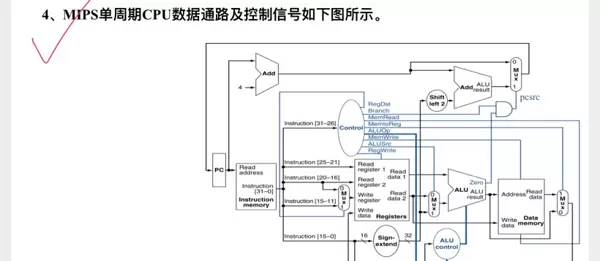

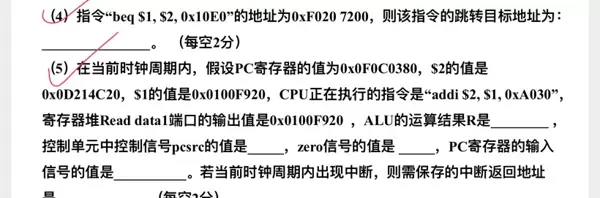

单周期指令数据通路分析

考查对典型单周期CPU结构的理解,尤其是各类信号路径与功能模块之间的连接关系。

(3)填空题:列出lw指令在执行过程中依次经过的关键功能部件

补充说明:本题虽未直接考查中断机制,但涉及异常处理相关内容,两者均需熟练掌握。

-

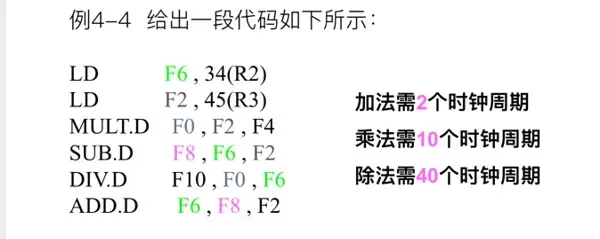

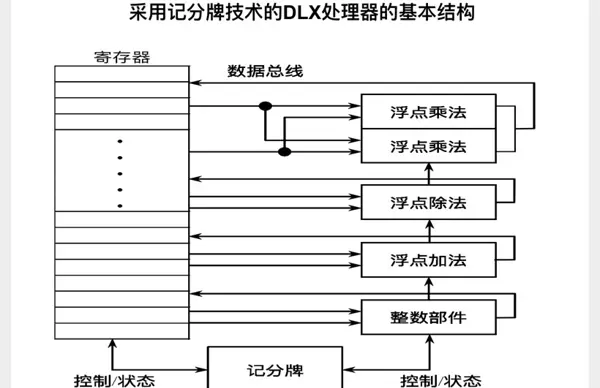

记分牌(Scoreboarding)调度分析

共考两问:第一问为第一条指令进入WR阶段之前的记分牌状态;第二问为MULT指令即将进入WR阶段前的状态更新。

注意:虽然例题仅覆盖硬件资源可用性、操作数就绪情况及读后写(RAW)冲突检测,但本次考试额外增加了写后写(WAW)冲突判断,需特别留意。

写在最后

本次考试让我颇为意外的是,平时练习中频繁出现的是beq、lw/st等常见指令,而大题却重点考查了addi、ori、andi这类相对冷门的立即数指令。看来传统重点可能正在发生转移。

希望后来者能以此为鉴,全面准备,不要局限于高频题型。祝各位考试顺利,稳拿高分!(^^)

扫码加好友,拉您进群

扫码加好友,拉您进群