TinyFPGA-Bootloader:基于 FPGA 的开源 USB 引导加载方案

在 FPGA 开发过程中,如何高效、便捷地将新的比特流写入设备始终是一个关键环节。尤其对于缺乏专用 USB-JTAG 编程器或追求低成本设计的开发板而言,传统烧录方式往往依赖额外硬件支持,流程复杂且成本较高。

TinyFPGA-Bootloader 正是为此类场景设计的一项开源解决方案。它以 IP 核的形式直接集成于 FPGA 逻辑资源中,实现一个完整的 USB 引导加载器功能,支持通过 USB 虚拟串口(CDC 类设备)向外部 SPI Flash 写入配置数据,从而完成 FPGA 配置镜像的更新与启动。

项目基本信息

- 名称:TinyFPGA-Bootloader

- 开源地址:https://github.com/tinyfpga/TinyFPGA-Bootloader(由 TinyFPGA 团队维护)

- 许可证:Apache-2.0

- 核心功能:利用 USB CDC 接口接收主机指令,由内嵌于 FPGA 的 bootloader 解析并操作 SPI Flash,实现比特流的加载与更新。

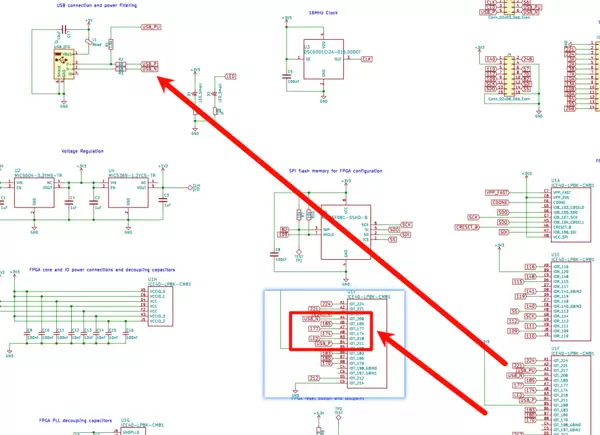

典型硬件要求

FPGA 板卡需满足以下基本条件以支持该 bootloader 正常运行:

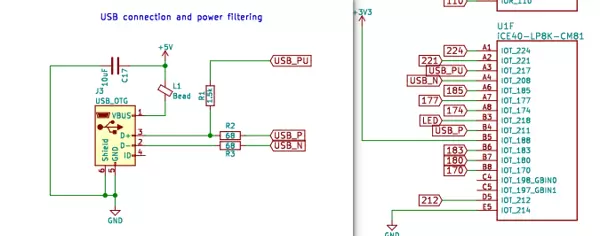

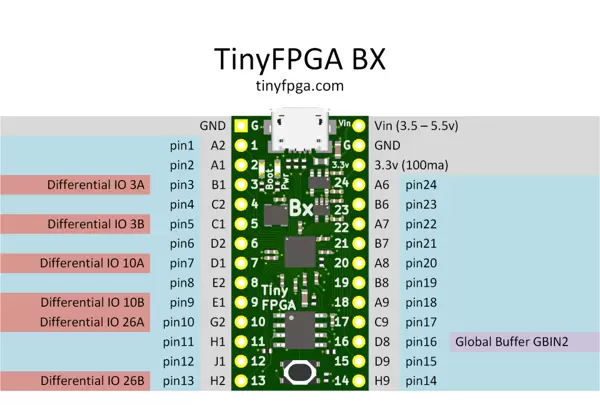

- 具备连接到 FPGA 的 USB_D+(USB_P)和 USB_D-(USB_N)信号,并工作在 3.3V 电平。

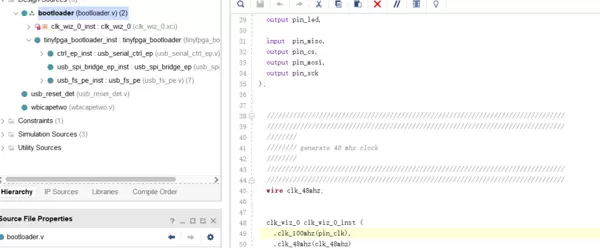

- 提供稳定 48 MHz 时钟源,可通过外部晶振配合 PLL 生成,用于驱动 USB 协议栈。

- FPGA 配置模式设置为从外部 SPI Flash 启动。

- USB_P 信号应连接 1.5 kΩ 上拉电阻,并建议通过控制信号 usb_pu 实现上拉使能管理。

- 推荐采用多镜像分区结构,便于区分 bootloader 与用户应用镜像。

主要特性优势

● 无需外置 USB 转 SPI 芯片

所有 USB 到 SPI 的协议转换均在 FPGA 内部逻辑实现,省去专用编程芯片,有效降低 BOM 成本与电路复杂度。

● 兼容虚拟串口编程方式

主机端识别为标准 CDC 串口设备,开发者可通过简单串口工具发送命令触发编程操作,学习与使用门槛低。

● 支持双镜像分区机制

SPI Flash 中划分独立区域存储 bootloader 和用户镜像。系统上电后由 bootloader 加载用户代码,也可进入更新模式重新烧写。

● 内置板卡元数据存储功能

利用 SPI Flash 的安全寄存器页保存板卡信息,如名称、FPGA 型号、硬件版本、序列号等,数据格式采用 JSON,便于通用软件自动识别不同硬件平台。

● 开放 SPI Flash 访问协议

通过 “Access SPI” 指令集,可在 USB 虚拟串口上执行任意 SPI 操作(读、写、擦除等),详细协议定义已在项目文档中公开,方便二次开发与调试。

示例支持与开发参考

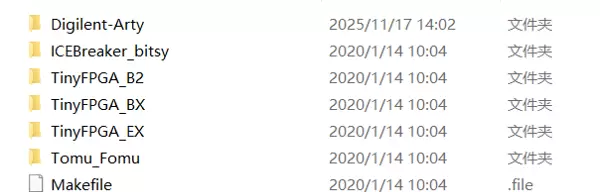

项目提供了多个目标开发板的参考实现,主要用于验证和快速部署:

- 原生支持 TinyFPGA 自家系列开发板,适配其硬件架构。

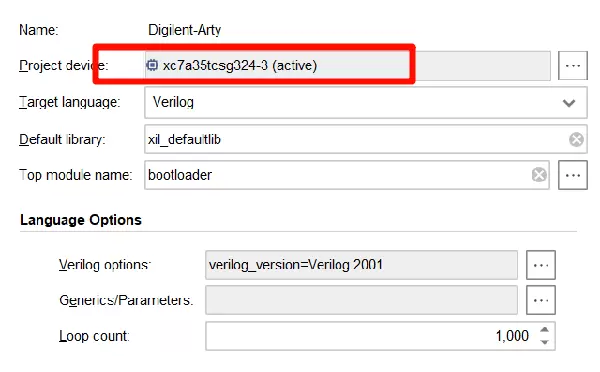

- 同时包含针对 Xilinx Artix-7 系列入门级开发板的移植示例,扩展适用范围。

打开对应工程文件即可查看实际运行 DEMO,注意建议使用 Vivado 2017 版本进行编译与综合,确保兼容性。

典型应用场景

- 低成本 FPGA 板卡设计:去除专用编程芯片,简化 USB 接口布线,优化整体成本。

- 教学与原型验证:学生或工程师可快速通过 USB 下载新配置,提升实验效率。

- 支持远程更新或多镜像切换的系统:适用于需要动态加载不同功能镜像或现场升级的可重构系统。

- 简化开发流程的硬件项目:实现“插入 USB → 打开串口 → 发送镜像”的极简烧录体验,提高开发迭代速度。

使用提示与注意事项

- 请确认 USB_P/N 信号走线正确,上拉电阻已接入,且 usb_pu 控制逻辑符合规范。

- 必须确保 FPGA 能够生成精确且稳定的 48 MHz 时钟供给 USB 模块,否则可能导致通信失败或设备无法枚举。

- SPI Flash 容量规划时应预留足够空间,涵盖 bootloader 区、用户镜像区及可能的数据存储需求。

- 当前 bootloader 不包含加密、签名或写保护等安全机制,相关功能需由用户自行扩展实现。

- 若计划将其集成至大型 SoC 或复杂 FPGA 工程中,需评估其对逻辑资源占用、时序路径以及与其他模块潜在干扰的影响。

总结

TinyFPGA-Bootloader 是一款高度实用、工程化程度高且完全开源的 USB 引导加载解决方案。它不仅显著减少了对外部编程器件的依赖,还极大简化了 FPGA 配置烧录流程。无论是用于教学演示、原型开发还是小批量生产,都表现出良好的适应性和易用性。

特别提醒:大容量比特流文件的下载耗时较长,请合理预期传输时间。

项目仓库地址

https://github.com/tinyfpga/TinyFPGA-Bootloader

扫码加好友,拉您进群

扫码加好友,拉您进群