多模态人工智能在EDA开发流程中的现状

摘要

现代半导体系统的设计是一项极其复杂的工程,其范围远超用寄存器传输级(RTL)语言对功能进行文本描述。电子设计自动化(EDA)流程本质上是多模态的,涉及丰富多样的数据格式,包括原理图、布局规划图、时序波形图以及热和电磁图等多物理场仿真结果。截至2025年8月,人工智能(AI)主要通过强化学习系统优化性能、功耗和面积(PPA),正显著进入EDA领域。然而,AI是否准备好处理更大规模、真正多模态和多物理场的任务,是一个关键问题。

本报告发现,尽管AI在优化数字设计流程的离散阶段已展现出显著的、可量化的成功,但其在真正的多模态理解和多物理场推理方面的能力仍处于初级阶段。来自Synopsys和Cadence的领先商业工具通过智能探索广阔的设计空间,取得了令人印象深刻的PPA收益。然而,从视觉图表进行整体推理、理解热-电磁效应等多物理场耦合约束,并将这种理解整合进优化循环的能力,仍是一个正在积极开发的前沿领域。在验证AI在这些复杂的多物理场领域准确性的公开基准测试和透明工作流程方面存在显著差距,这表明一个完全多模态的AI设计伙伴愿景尚未成为现实。

第一章 引言:半导体设计超越文本

半导体系统的开发从根本上是一个多模态过程。虽然RTL代码是芯片逻辑的关键文本表示,但它只是整个复杂拼图中的一小块。从概念到硅片的旅程涉及不同信息模式之间的持续转换。工程师们依赖大量图形和非文本格式来构思、实现和验证设计。这包括框图、时序波形图、状态图、布局规划图、物理版图以及热图等,每一种格式都传达了复杂的空间、时间或物理关系,这些关系用纯文本表达是繁琐甚至不可能的。

在这个语境下,“一图胜千言”的说法是高度保守的。例如,布局规划图直观地传达了影响性能的邻近性、层次结构和物理约束。同样,时序图捕捉了信号随时间变化的动态相互作用。为了让AI真正彻底改变EDA工作流程,它必须超越早期大型语言模型(LLM)所见的以文本为中心的初步成功,发展出理解、推理和生成这些多样化数据格式的能力。

这一挑战因两个主要因素而加剧。首先,AI模型的开发在历史上是分散的,图像识别、文本处理和逻辑推理分别由不同的系统处理。将这些不同的系统整合成一个有凝聚力的整体,在计算负载和功耗方面带来了重大挑战——这对半导体行业至关重要。其次,或许更为深刻的是物理学的挑战。芯片性能受电磁学、热力学和量子力学等复杂、相互交织的定律支配。当今大多数AI系统缺乏对这些物理原理的深刻、直观理解,使得多物理场推理成为实现全面自动化的巨大障碍。本报告评估了截至2025年中期多模态AI在EDA中的现状,审视了其当前的成就、仍然存在的重大障碍以及未来的道路。

第二章 当前格局:AI作为PPA优化引擎

截至2025年,AI在EDA中最成功的应用是作为数字实现流程中强大的优化引擎。领先商业工具的主要重点是在广阔、高维度的芯片设计解空间中导航,以实现卓越的PPA结果。

2.1 商业AI-EDA实施

EDA市场领导者大力投资于将AI整合到其核心工具链中,明确专注于自动化从RTL到GDSII的流程。

Synopsys 与 DSO.ai™: Synopsys 提供了一套涵盖整个设计栈的AI驱动工具套件。其旗舰产品是 DSO.ai (设计空间优化AI),它利用受DeepMind AlphaZero启发的强化学习来自主搜索最优设计解决方案。它用于优化芯片实现,以及执行功耗仿真和热分布分析等复杂任务。案例研究证明了其有效性:据报道,意法半导体(STMicroelectronics)在Arm CPU核心实现上提升了3倍生产力;三星(Samsung)使用它完成了高性能移动芯片的流片;SK海力士(SK Hynix)通过使用DSO.ai优化逻辑单元布局,在闪存芯片上实现了5%的占位面积缩减,同时逻辑单元面积本身减少了约15%。

Cadence 与 Cerebrus™: Cadence的主要AI产品是 Cerebrus,这是一个AI驱动的工具,可自动优化IC设计以满足PPA目标。它利用机器学习来自动化和扩展整个数字芯片设计流程,智能调整工具设置以实现卓越结果。Cerebrus深度集成于Cadence数字流程中,包括Innovus实现系统和Genus综合解决方案。与德州仪器(Texas Instruments)在宏单元主导的SoC设计上进行的一项广泛案例研究显示了显著的PPA改进,包括在先进制程CPU设计上实现了7.37%的标准单元面积收益、总负时序裕量(TNS)提高了75%,以及违规路径数量减少了26倍。

其他关键举措: 除了两大巨头,其他重要参与者也在推动该领域发展。谷歌(Google) 因将AI用于芯片物理设计而闻名,其“Google Brain”计划以及 AlphaChip 学习方法已被用于优化多代张量处理单元(TPU)的布局。英伟达(NVIDIA) 正在利用其自身硬件,合作伙伴如NewSilicon在GH200 Grace Hopper超级芯片上部署AI驱动的EDA栈,实现了设计和验证性能高达15倍的提升。开源努力也在涌现,例如 Aitomatic 的 SemiKong(面向半导体行业的大语言模型)和 ChipNeMo(将LLM应用于EDA脚本生成和错误分析等任务)。

这些工具代表了从手动“调参”到自主、目标驱动优化的范式转变。然而,它们的主要操作模式涉及处理结构化数据和参数集以优化数值PPA目标,而非理解手绘原理图等非结构化的多模态输入。

第三章 多物理场前沿:AI的推理鸿沟

芯片的物理现实——热热点影响时序,电磁干扰破坏信号——为EDA中的AI带来了下一个巨大挑战。芯片的版图不仅仅是几何排列;它是复杂相互作用物理场系统的表示。成功驾驭这一点需要AI具备强大的物理学理解能力,而这恰恰是当前模型明显薄弱的领域。

3.1 行业认知与工具开发

EDA供应商认识到多物理场分析的至关重要性。

- Synopsys 正在与 Ansys 合作,将系统级热-机械仿真集成到设计流程中,旨在提高极端环境下设备的可靠性。其 PrimeTime-SI (PTSI) 信号完整性黄金时序分析工具是考虑IR压降对静态时序多物理场影响的分析流程的一部分。

- Cadence 推广其“EDA 2.0”解决方案,其中包括 “Optimality™ Multi-Physics” (多物理场智能系统探索器),并与用于热分析的 Celsius Studio 集成。该公司更广泛的系统设计与分析(SDA)产品类别被定位为一个涵盖电磁和热分析的综合多物理场平台。

- Siemens EDA 通过其 Calibre 平台应对这些挑战,该平台提供多物理场验证解决方案,旨在分析和缓解热影响与电气行为之间的相互作用,特别是在复杂的3D-IC设计中。

虽然这些工具为多物理场仿真提供了底层引擎,但将它们集成到像DSO.ai或Cerebrus这样的AI驱动优化循环中的关键步骤仍然不透明。没有来自官方的、详细的公开工作流程图展示这些AI优化器究竟如何摄取和推理耦合的多物理场约束。

3.2 基准测试与验证的空白

评估AI应对多物理场任务准备程度的一个核心问题是严重缺乏标准化的公开基准。

- 通用物理基准: 像 UGPhysics 和 PHYSICS 这样的学术基准测试LLM在本科和博士级别物理问题上的表现。结果是令人清醒的:即使2025年最先进的模型,其准确率也低于50%,突显了科学推理方面的根本性差距,更不用说半导体设计中应用的、耦合的物理学了。

- EDA特定基准: ChiPBench 基准旨在评估基于AI的芯片布局算法在端到端PPA指标上的表现。其发现表明,虽然一些AI算法在中间指标上表现良好,但它们常常无法优化最终的PPA,这表明它们可能是在局部优化,而缺乏对整体设计的、具备物理感知的全局理解。

- 缺乏商业指标: 广泛搜索Synopsys PrimeTime-SI或Cadence Optimality Multi-Physics等商业工具中热-电磁协同优化的定量、第三方或数据手册公布的精度指标,均未果。最接近的数据点是PrimeTime时序分析与SPICE在5纳米工艺上的相关性研究,显示标准偏差为1.6%,但这并未涉及耦合多物理场精度这一更为复杂的问题。

这种“验证空白”表明,虽然业界正在构建必要的仿真基础设施,但AI自主且准确地协同优化这些复杂物理效应的能力尚未成为成熟的、可验证的能力。

第四章 计算成本与工作流集成的挑战

为了使多模态AI具有实用性,它必须在计算上高效并无缝集成到现有的EDA工作流程中。同时运行用于文本、视觉和物理推理的多个大规模AI模型所产生的巨大计算开销是一个主要障碍。

业界正在积极寻求解决方案来减轻这种负载。技术手段包括算法优化,如 L-Mul算法,它用整数加法替代能耗密集的浮点乘法;以及模型优化方法如 动态剪枝(dynamic pruning) 和 输入压缩(input compression),可实现50-60%的模型大小缩减。此外,正在开发先进方法,如 动态多模态融合(dynamic multimodal fusion) 和稀疏注意力机制,以显著降低计算成本和推理延迟,而不会造成重大精度损失。在硬件方面,正在部署像 NVIDIA的GH200 Grace Hopper超级芯片 这样的专用硅片,专门用于加速这些高要求的AI驱动EDA工作负载。

即使有了这些进步,将AI集成到视觉化和直观的工作流中仍然是一个挑战。理想的多模态AI应通过图表和视觉表示与工程师互动。然而,像Cadence Cerebrus这样的领先工具的官方文档和用户指南缺乏展示如何实现多物理场或多模态约束的详细可视化工作流程图。这强化了这样一种观点:当前的AI更多地充当“黑盒”优化器,操作预定义的工具“旋钮”和结构化数据,而不是一个能够就视觉呈现的设计概念进行推理的协作伙伴。

第五章 可量化影响:AI当前的贡献领域

尽管在真正的多模态方面存在挑战,但AI在数字领域对PPA及相关指标的影响是毋庸置疑且有据可查的。

5.1 PPA与电源噪声分析中的实测收益

2024年和2025年的案例研究和基准测试清晰地展示了在先进工艺节点上取得的性能收益。

- 整体PPA: 在5纳米移动CPU设计中,AI驱动的优化实现了14%的性能提升和7%的漏电功耗改善。对于其他5纳米设计,AI在GPU上实现了9%的总功耗优化,在AI加速器上实现了8%的总功耗优化。

- 信号与电源完整性: 虽然在已发表文献中缺乏针对复杂“电源噪声耦合分析”的直接比较(查询10, 17, 18, 19),但相关领域的指标显示了AI的强大性能。

- 信号完整性: 与传统方法相比,AI驱动的优化方法在信噪比(SNR)上展示了高达40.8%的改善,并将布线拥塞减少了40.8%。

- 时钟树综合(CTS): 基于AI的CTS已被证明可将信号偏斜(skew)较传统方法减少多达50%,从而带来更好的时序性能。

- 功耗降低: 在各种设计中,AI方法实现了显著的功耗节省,一些组合AI模型将总功耗降低了近19%。

这些数据表明,通过智能探索数百万种设计实现选项,AI在优化数字设计领域内可测量的、相互依存的指标方面非常有效。然而,这些成功主要发生在一个可以将“物理”抽象为明确定义的模型和成本函数(例如时序、功耗、拥塞)的空间,而不是在热和电磁现象深度耦合、非线性的世界中。

第六章 结论与未来展望

截至2025年8月,AI在EDA开发流程中的应用呈现出一幅分化的图景。一方面,AI已被证明是数字实现领域PPA优化的变革性技术。像Synopsys DSO.ai和Cadence Cerebrus这样的工具通过利用强化学习自动化复杂的设计空间探索任务,在性能和功耗方面带来了实实在在的两位数百分比改进。

另一方面,真正多模态AI的更广阔前景——能够流畅地解释原理图、与工程师就设计意图进行交流、并针对深度耦合的多物理场约束进行协同优化——在很大程度上仍处于展望阶段。关键挑战是巨大的:

- 物理理解: 当前的AI模型缺乏强大的推理能力来精确建模和优化相互交织的热、电磁和机械应力效应。

- 缺乏验证: 供应商或独立实验室严重缺乏公开的、定量的基准测试来验证AI驱动的多物理场协同优化的准确性。

- 工作流集成: 将AI集成到可视化、直观且真正多模态的工作流中尚未实现,当前系统运行起来更像强大但不透明的优化引擎。

前进的道路需要在多个方面进行集中创新。开发专门针对多模态工程数据进行训练的基础模型、在AI物理推理方面取得突破、以及为多物理场验证创建行业标准基准测试,都是必不可少的后续步骤。最终目标是将AI从“调参器”进化为真正的设计伙伴,能够理解并参与到半导体设计这一复杂而创造性过程的每一种模态中。

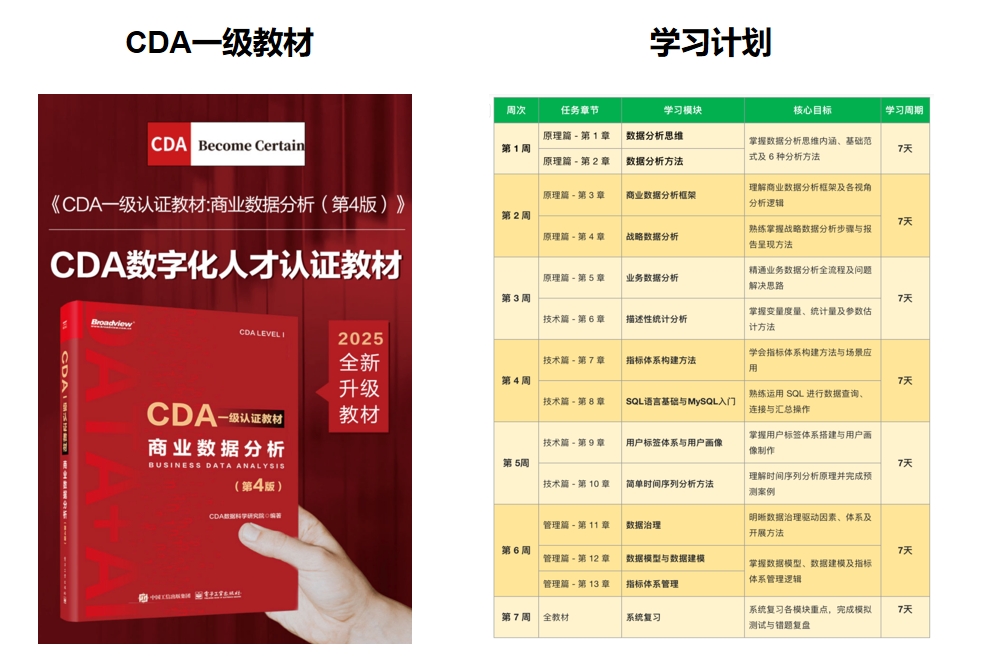

推荐学习书籍 《CDA一级教材》适合CDA一级考生备考,也适合业务及数据分析岗位的从业者提升自我。完整电子版已上线CDA网校,累计已有10万+在读~ !

扫码加好友,拉您进群

扫码加好友,拉您进群